هیسترزیس ناشی از تله سطحی در FET نانوسیم InAs – تجزیه و تحلیل گرادیان چگالی – کامسول

Surface-Trap-Induced Hysteresis in an InAs Nanowire FET — a Density-Gradient Analysis

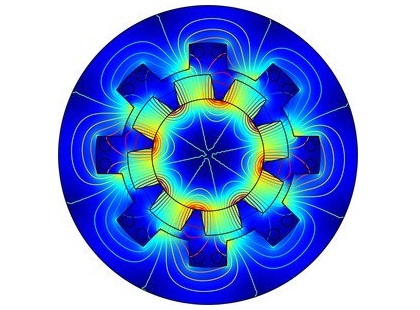

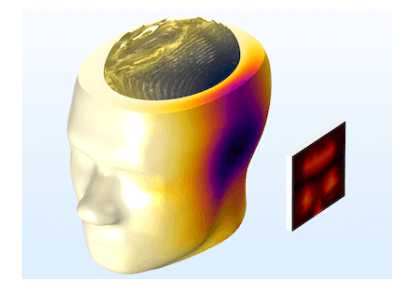

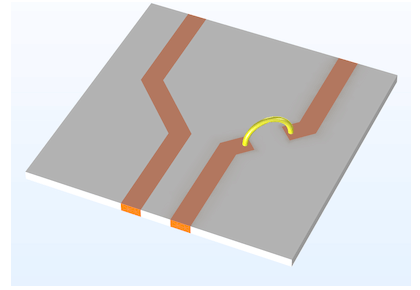

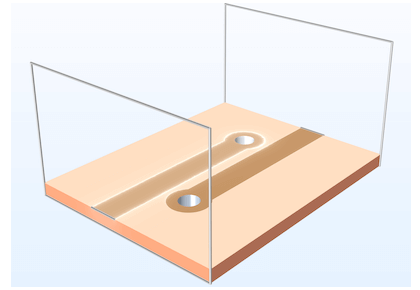

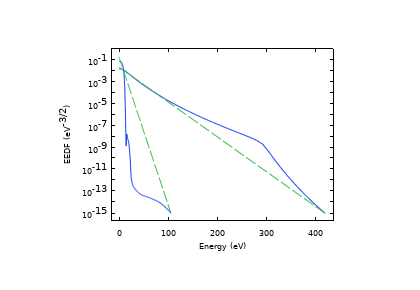

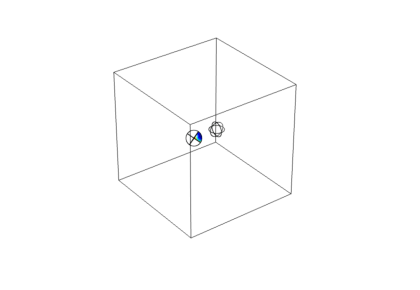

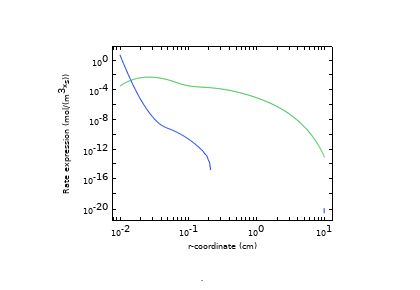

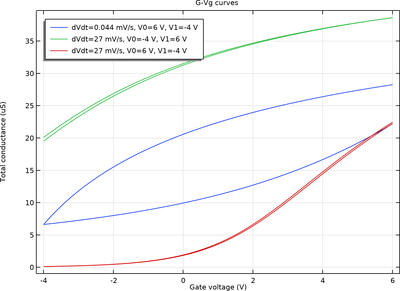

این آموزش پسماند منحنیهای رسانایی- گیت-ولتاژ (G-Vg) یک FET نانوسیم InAs را با استفاده از تئوری چگالی- گرادیان برای افزودن اثر محصور شدن کوانتومی به فرمولبندی رانش- انتشار معمولی، بدون افزایش زیاد هزینه های محاسباتی هیسترزیس توسط اثرات شارژ دینامیکی تله های رابط نیمه هادی-اکسید سریع و آهسته توزیع انرژی پیوسته و از هر دو نوع دهنده و گیرنده ایجاد می شود. احتمال جذب به صورت گرمایی با ارتفاع مانع که با سطح انرژی تله تغییر میکند، مدلسازی میشود. رفتار کیفی و ترتیب بزرگی منحنیهای G-Vg محاسبهشده تحت شرایط مختلف افزایش ولتاژ به خوبی با نتایج شبیهسازی و آزمایش موجود در ادبیات مطابقت دارد.

This tutorial analyzes the hysteresis of the conductance-gate-voltage (G-Vg) curves of an InAs nanowire FET, using the density-gradient theory to add the effect of quantum confinement to the conventional drift-diffusion formulation, without a large increase of computational costs. The hysteresis is caused by the dynamic charging effects of fast and slow semiconductor-oxide interface traps of continuous energy distributions and of both donor and acceptor types. The capture probability is modeled as thermally activated with a barrier height that varies with the trap energy level. The qualitative behavior and the order of magnitude of the computed G-Vg curves under various voltage ramping conditions agree well with simulation and experiment results found in the literature.

- COMSOL Multiphysics® and

- Semiconductor Module

- لینک دانلود به صورت پارت های 1 گیگابایتی در فایل های ZIP ارائه شده است.

- در صورتی که به هر دلیل موفق به دانلود فایل مورد نظر نشدید به ما اطلاع دهید.

برای مشاهده لینک دانلود لطفا وارد حساب کاربری خود شوید!

وارد شویدپسورد فایل : پسورد ندارد گزارش خرابی لینک